さて、前回の最後に「キャパシタ」というのがでてきました。その働きは電気をためたり出ししたりでしたね。ママは半導体が記憶する、ということに思い当たります。

ふと考え込むママ。

ママ、なんかわかってきてます。これこそ集積回路が発達してきた理由ですね。

半導体の記憶再び

「カラン、コロン」

今日もカモが、いや失礼お客様がやってきました。

メモリーとは

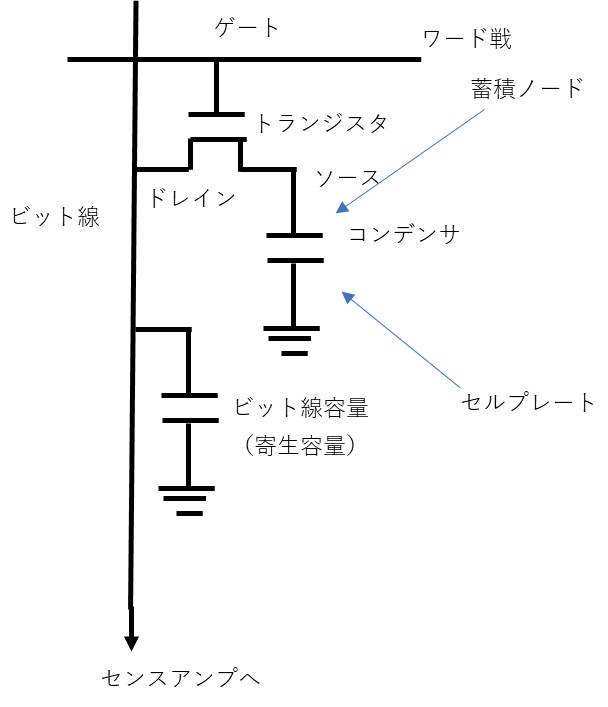

以前にメモリーの構造については紹介しました。(参照:半導体の記憶とは?)今回は記憶の時に電気をためるコンデンサと電気の出し入れをつかさどるトランジスタの集積化(一つに集めること)について紹介していきます。

DRAMについては以前紹介しましたが、もう一度ここで復習します。DRAMとはダイナミックアクセスメモリーの略でダイナミックは動的という意味でした。時々メモリーをリフレッシュするためにアクセスする記憶装置ということになります。(参照:半導体の記憶とは?)

なぜ時々メモリーをフレッシュさせる必要があるかと言えば、少しずつ電気が漏れるからです。(参照:半導体の記憶とは?)

メモリーの役割はデータの保持、読みだし、書きこみになります。具体的には保持の状態がトランジスタ「OFF」でコンデンサの電気を逃がさないようにします。

書き込みはビット線を書き込み情報に合わせた電位に固定してトランジスタを「ON」にして、ビット線と同じ電位にすることでできます。読み出しはトランジスタを「ON」、ビット線に電位が変化したのを検出します。

しかしながら、コンデンサに蓄えられている電気(電荷)はわずかなため、確実に検出するためにはコンデンサの容量がある程度大きくする必要があります。どれくらい必要かというと、ビット線上にできてしまう寄生容量の10倍程度が必要です。

導線が二本あるとその間に電位差があった場合にはコンデンサのように電気をためてしまいますが、このような状態を寄生容量といいます。

また、センスアンプとはコンデンサからのデータ読み取り電圧を増幅させるための回路です。

また、セルの大きさは集積化に伴って小さくしていく必要がありますが、コンデンサ(キャパシタ)の容量は導体の面積に比例し、導体間の距離に反比例するため、容量を同じにしていくのはかなり困難な課題です。(参照:半導体 脇役?たち・・・集積回路用抵抗、キャパシタについて)

同じ面積、導体間の距離で容量を大きくするためには、挟まれる誘電体を誘電率の大きいものするという方法もありますが、現段階では際立ったものを使用できるようにはなっていません。

これらを踏まえて、ここからは、キャパシタだけでなく、メモリセルという単位で考えていきます。セルとは日本語では細胞の意味で、ここではトランジスタとキャパシタを合わせた一つの記憶素子のことです。(参照:半導体の記憶とは?)

プレーナ型セル

プレーナとは「平に削られた」ことです。つまり表面が平坦な構造をしたセルです。以前にプレーナ型トランジスタで紹介しました。(参照:半導体 エピタキシャルの歴史~シリコンウェハーの作り方)

メモリー数が4~256kまではこの構造で使用されてきました。これらはトランジスタや蓄積ノードがシリコンウェハー上に作られています。

プレーナ型セルの構造を以下に示します。

トレンチ型セル

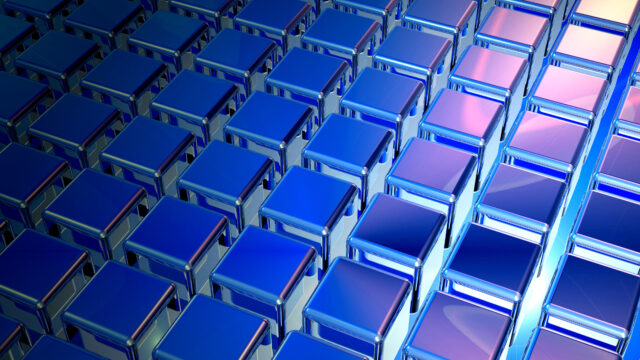

メモリーのサイズがメガビットまで必要な時代になると、それまでのプレーナセルでは追いつかなくなってきます。そこで考えられたのが、三次元構造です。三次元構造の特徴はセルの大きさを変えずに電極の面積を増やせる、ということです。

そんな中トレンチ型セルが開発されました。トレンチとは塹壕や堀といった意味で、シリコンウェハーの上ではなく中の方にキャパシタを作り出します。

トレンチ型は下図のようにシリコンウェハーに溝を掘ってキャパシタを形成しています。

スタック型セルとは

トレンチ型はシリコンウェハー内に溝を作って面積を増やしました。スタック型はその逆と言えるかもしれません。

スタックとは「積み重ね」の意味です。つまりスタック型とは、「積層型」とも言われます。

MOS構造のキャパシタは、シリコン内で発生するキャリア(電子や正孔)の影響を受けて、高集積化していくと、キャパシタに保持される電気量が減少していきます。そのため、スタック型は蓄積ノードがシリコン基板から離すように作られています。

また、トランジスタ形成後にキャパシタを作り込むため、蓄積電極、絶縁膜、プレート電極の材料選択に自由度が増すため、誘電率が高い物質を選択できるといった利点があります。

まとめ

DRAMの歴史は工夫の連続です。これからまだまだ進化していきのでしょう。現段階では一トランジスタ1キャパシタの組み合わせがDRAMの基本ですが、これもまた将来変わるのかもしれません。

DRAMの構造の変化は住宅事情に似ているかもしれません。平屋では住宅を賄いきれず、地上高くマンションを建てたり、地下に居住を求めたりと。

そう考えると、人間はメモリーの中の電荷(電気)ということになりますね。ワード線やビット線に操られて家を出たり、入ったり・・・。家のサイズが大きくなれば、そこに詰め込まれる人もふえることでしょう。

昔の日本の家は海外の人から「ウサギ小屋」といわれていました。DRAMの発想をまねて、再びそんなことにならなければよいのですが・・・。

お問い合わせ

参考図書: 佐藤淳一著「よくわかる半導体デバイスの基本と仕組み」株式会社秀和システム2021年215p 前田和夫著「はじめての半導体プロセス」株式会社技術評論社2021年291p

参考サイトhttps://www.jstage.jst.go.jp/article/ieejjournal1888/108/5/108_5_397/_pdf/-char/ja 「大容量DRAMプロセス技術の展望」2022年12月14日